Profile:

Experienced in IC (Integrated Circuits) digital design with more than 22 years of experience in designing, verifying and validating best-in-class ASIC and FPGA digital IPs as well as embedded systems.

I performed over a broad technical area containing video processing, signal treatment and digital electronic design.

Expert in RTL (VHDL/Verilog), in synchronous, high speed and low power digital design, I achieved on-silicon successful development of several digital modules and systems.

The target applications were digital television, application processors, defense, EDA (Electronic Design Automation) and research.

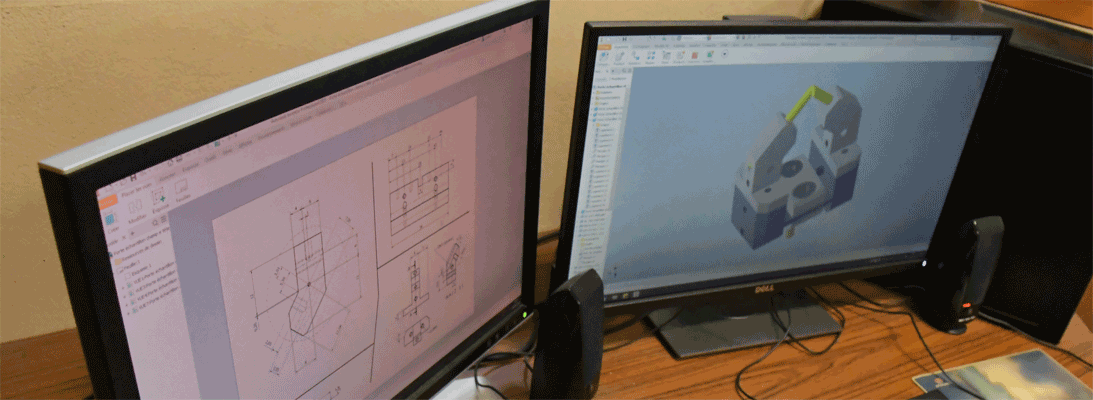

Expert in CAD (Computer Aided Design) and IC digital design, I have gone through the entire ASIC and FPGA digital design flow from specification to layout passing by functional verification and logic synthesis. I used state-of-the-art EDA tools and methodologies.

I have in-depth knowledge of front-end digital design flow consolidated with embedded systems design, PCB (Printed Circuit Board) design as well as NQR/NMR real-time digital acquisition systems and instrumentation development and testing.

I had the opportunity to work in multinational, multi-site, cross-cultural and multi-disciplinary environments. I contributed individually and collectively to important and decisive projects. I have nice achievements and success stories.

I played also key roles in technical support, coaching and mentoring.

Research activity:

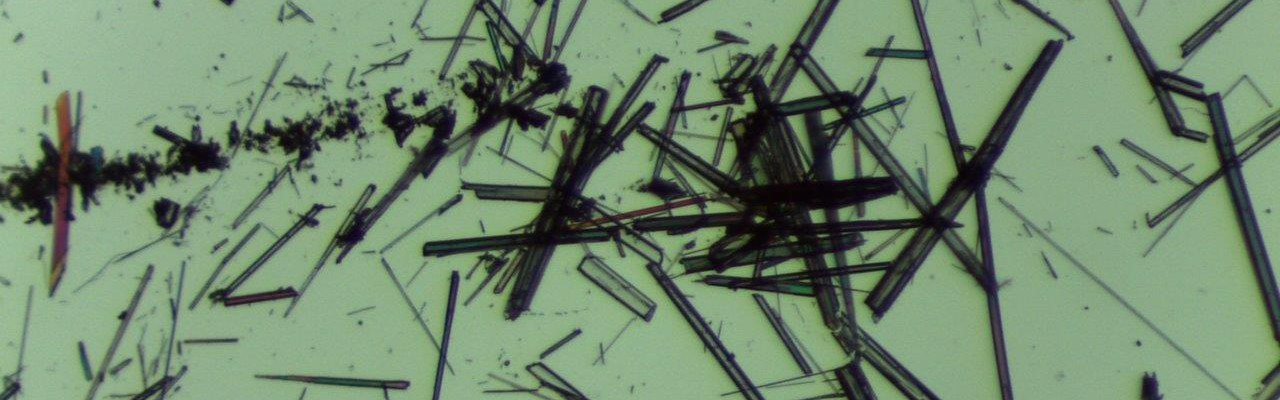

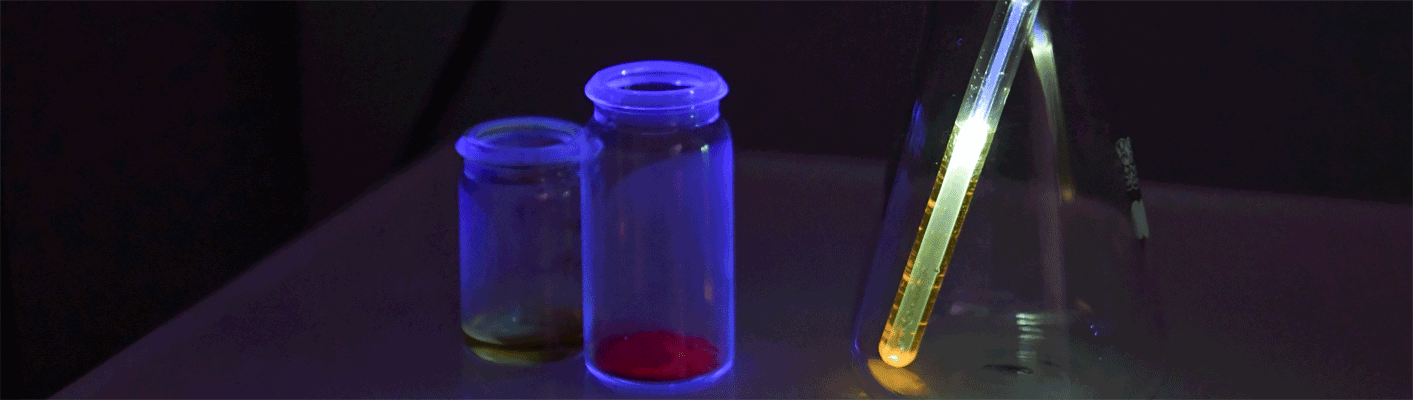

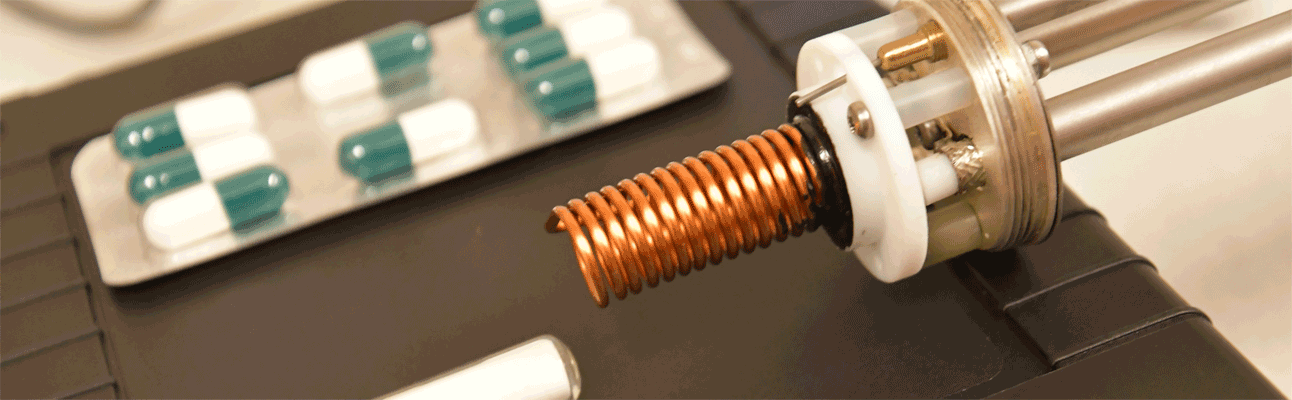

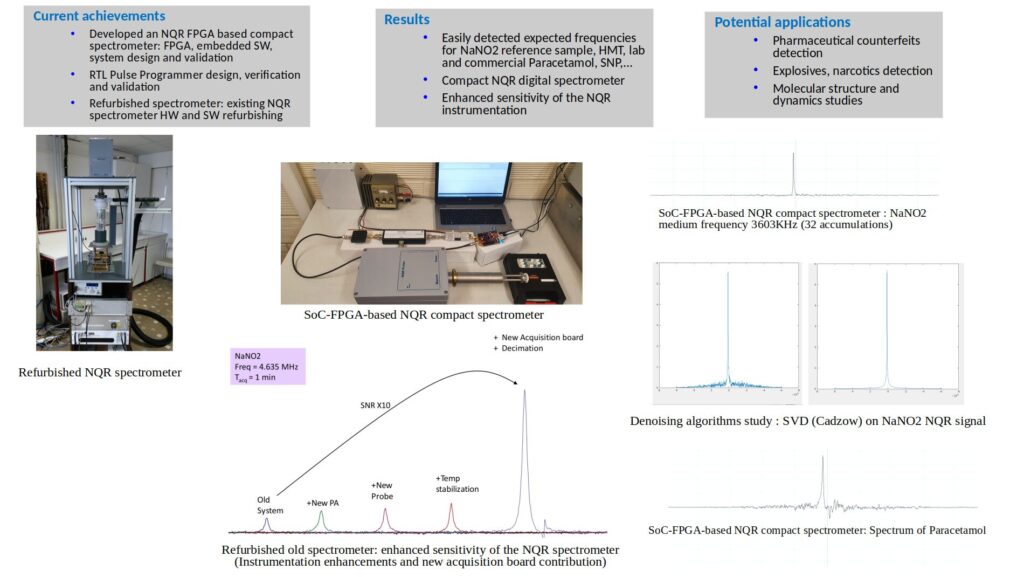

The NQR technique though it suffers from weak sensitivity has a wide spectrum of possible applications like drugs analysis, molecular structures studies and detection of counterfeit medicine, narcotics and explosives.

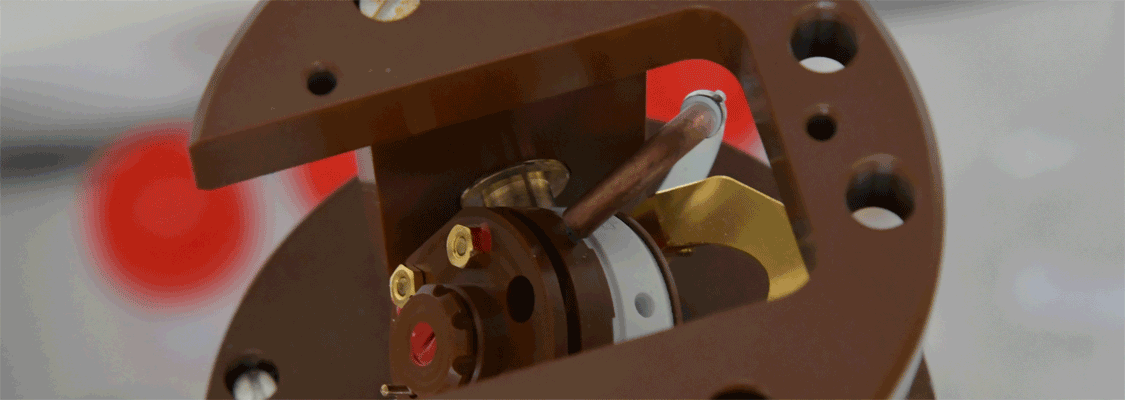

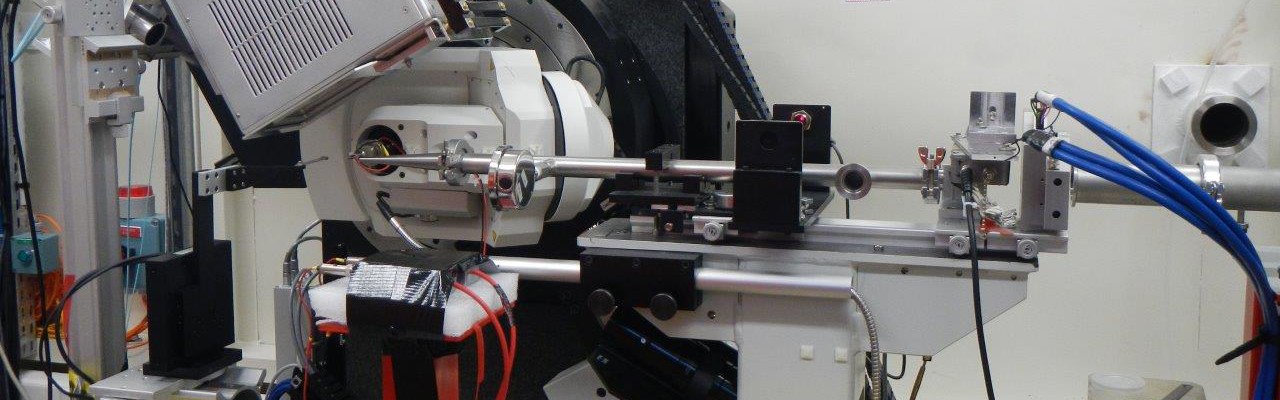

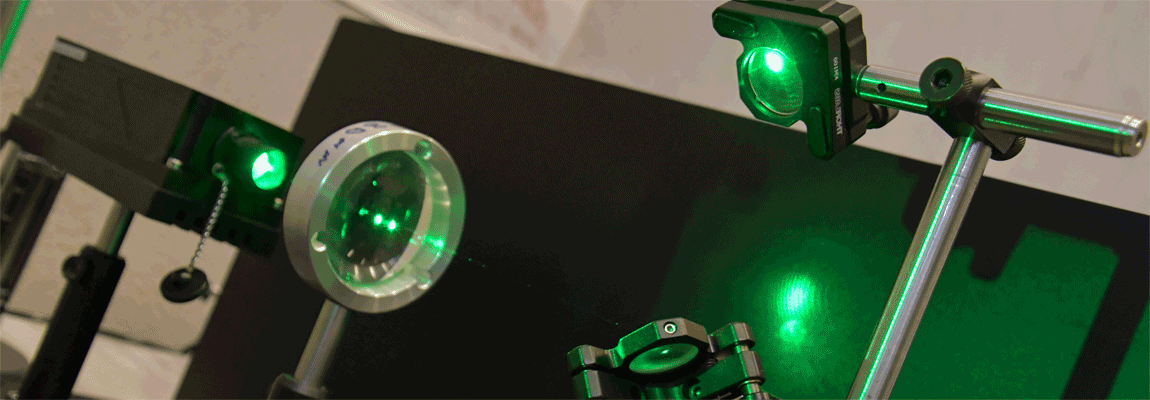

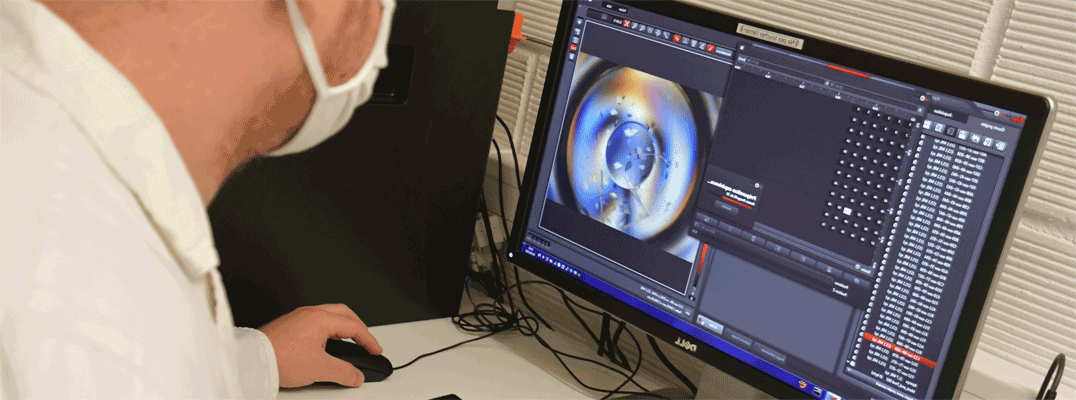

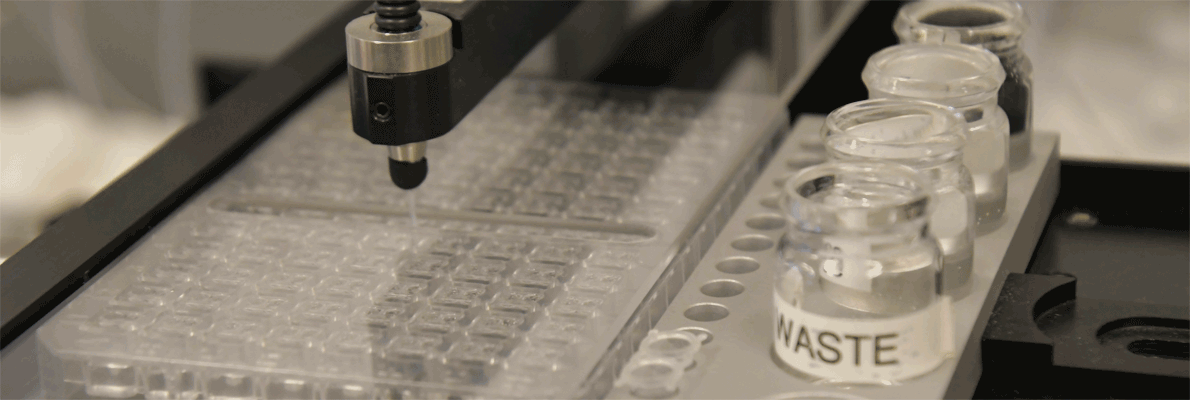

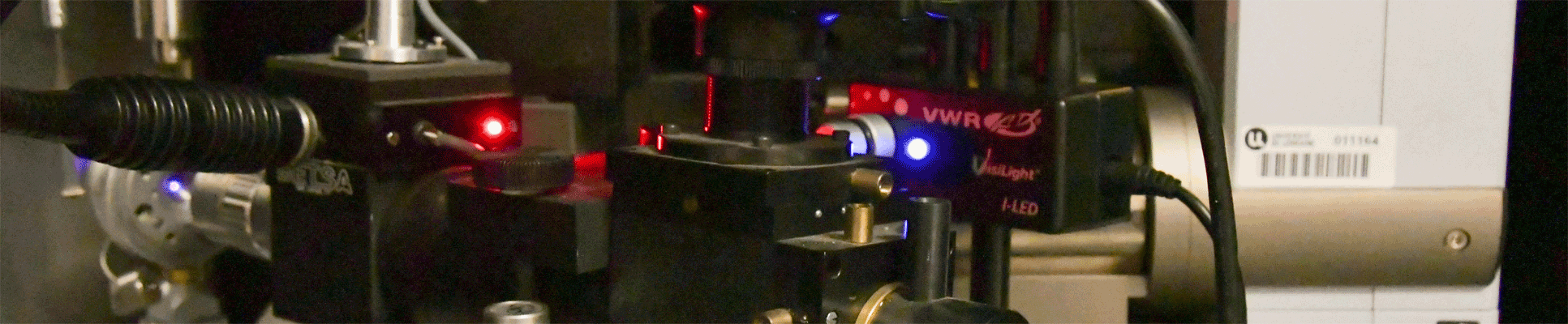

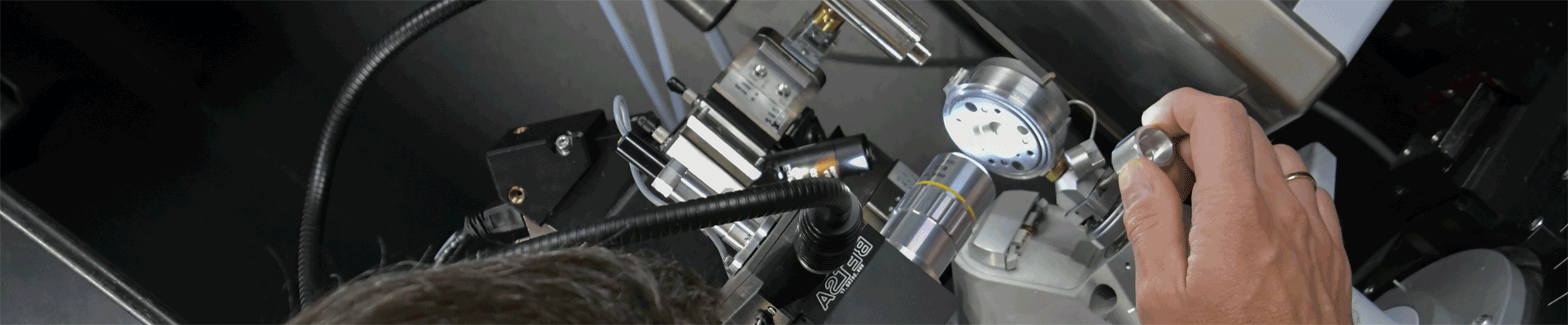

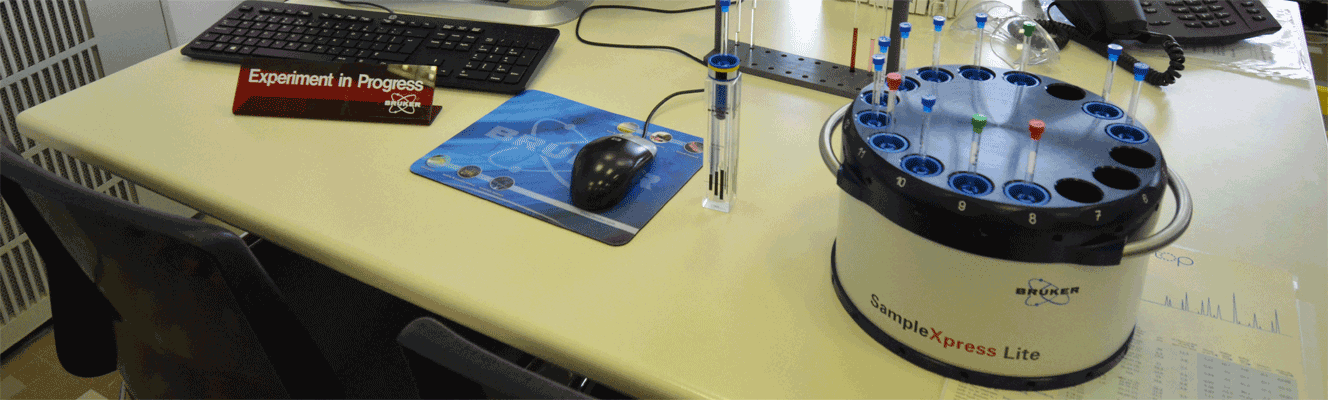

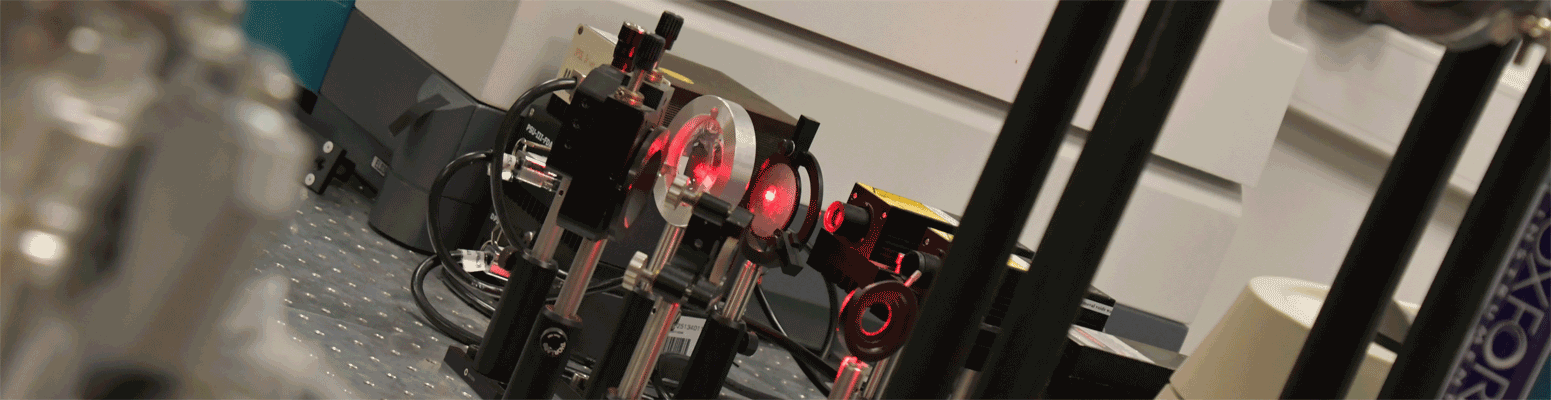

My major research activity, which aims to enhance the sensitivity of NQR/NMR instrumentation, is focused on two axes, the first one is FPGA/SW/System design and validation dedicated to the development of innovative and original NQR/NMR portable and miniaturized spectrometers.

The developed systems, hence embark digital and analog electronics as well as embedded software targeted to the detection and processing of weak RF signals especially for NQR technique.

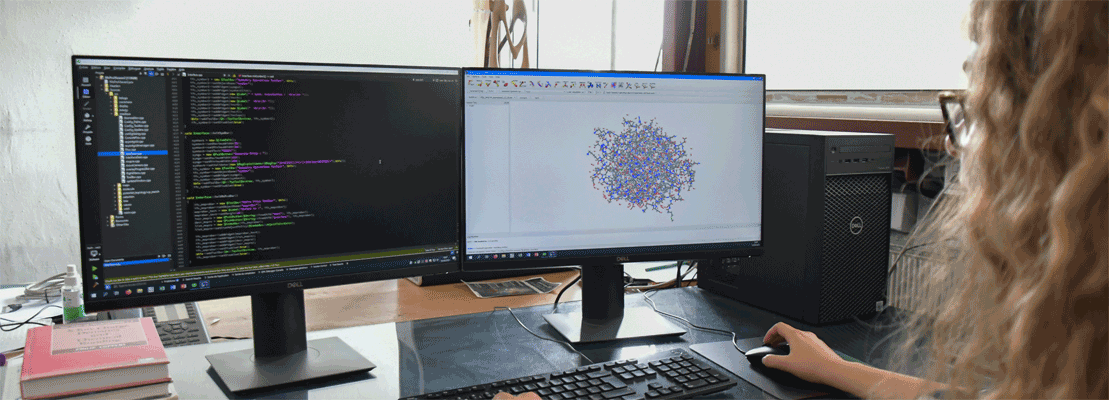

My second research interest is the definition, implementation and validation of signal de-noising techniques for NQR/NMR signal. The implementation could be on SW or on digital hardware target (SoC-FPGA). The chosen techniques could be classical algorithms like SVD, PCA digital filtering, NMR per-processings, or new AI-based methods.

The so far obtained results, using the developed systems, are very promising since we now easily detect the expected frequencies for reference samples as well as for commercial ones (e.g., commercial and lab synthesized Paracetamol).

Indeed, the SNR of the system was significantly enhanced compared to old system developed in the team (x10 thanks to refurbishing and new acquisition using oversampling and then x2,5 thanks to SoC-FPGA design and integration).

These encouraging results are also paving the way for portable NMR.

Education :

1994-1997 : Classes préparatoires (Math Sup et Math Spé) au lycée Moulay Youssef (Rabat)

1997-2001 : École Mohammedia des Ingénieurs (Rabat), (Premier de l’option électronique et télécommunications)

2001 : Diplôme d’ingénieur d’état en électronique et télécommunications (EMI)

2024 : Obtention du grade de Docteur de l’université de Lorraine mention “Systèmes Électroniques”

Professional carrier :

Since 2015 : CNRS

Research Engineer (Nancy) : (Permanent position)

NQR instrumentation design. Sensitivity enhancement and denoising. Research and valorization.

Technologies: {VIVADO, SDK, Embedded Linux, Zynq AP SOC, RF preamplifiers/Amplifiers, IQ Modulation/Demodulation, ADCs, NMR, NQR, General Electronics}.

2013 – 2014 Cadence :

Lead Application Engineer (Munich) :(Permanent position)

-Pre-sales campaigns and customer support on Cadence tools (Front-End Digital Design)

-Customer education on High Speed and Low Power intended design techniques

Technologies: {IUS, RTL Compiler, Encounter Conformal , Encounter EDI, DFT, CPF Low Power flow}.

2010-2013 MASCIR :

Senior Embedded Systems Engineer (Rabat): (Permanent position)

Architecture enhancement, PCB design, FPGA design and validation of a complete embedded system (HDI Boards + FPGA+ hundreds of SMT components) : CMOS/CCD Micro-camera HD video quality demonstrator

Technologies: {VHDL, FPGA, Altera Cyclone II & III, Micro-Camera, PCB Design}.

2008-2009 : Atos (ex Amesys)

Senior FPGA Design Engineer (Rabat/Aix-En-Provence) (Permanent position)

FPGA design and verification of an RF communication system (Spectrum analyzer and bands detector)

Technologies: {VHDL, FPGA, DSP, Modelsim, Functional verification, Xilinx Virtex 5}.

2007 -2008 EASII-IC :

Senior ASIC Design Consultant (Nice) (Permanent position)

ASIC Design Consultant at Texas Instruments

Technologies: {DFT, ASIC Front-end digital Design}.

2001-2007 : ST-Microelectronics :

Senior ASIC Front-End Digital Design Engineer (Rabat/Grenoble) (Permanent position)

Actively contributed to the development of several Digital TV Decoders and Application Processors (STV3550)

(Digital Video Output Stage) , STV3600, STV2310(Video Scaler), Nomadik(Host Port Interface), …)

Technologies: {VHDL, ASIC, Specification, RTL testbench, Synchronous Digital Design, Methodology, AVP(Architectural Verification pattern), Simulation (Cadence Ncsim), Logic Synthesis (Synopsis Design Compiler), STA (Synopsis Primetime)}.